## Top-gate Inserted Dual-gate Indium-Gallium-Zinc Oxide Thin-Film Transistors and Prospects for Flexible Applications

Yuqi Wang\*, Zhihe Xia\*, Man Wong\*

\* Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Hong Kong, China

In this study, dual-gate (DG) thin-film transistors (TFTs) based on indium-gallium-zinc oxide (IGZO) with inserted top-gate electrode has been developed. The transfer characteristics of such DG TFTs were measured, and the source/drain (S/D) resistance was extracted. Overall, the modulation of threshold voltage ( $V_{\text{th}}$ ) was given by applying a series of top-gate voltages ( $V_{\text{TG}}$ ). There performances are compared with the state-of-art DG technologies.

The electrical performances of DG TFTs have been compared with the single-gate (SG) TFT technologies of both bottom-gate (BG) and top-gate (TG) structures. It is concluded that DG technology have advantages compared to SG for the application of circuit design, sensor achievement and other flexible integration systems, with almost doubled effective field-effect mobility, an extra independently adjustable port for  $V_{\rm th}$  control, and much better electrical stability behaviors by applying comparable TG and BG voltages which can neutralize electric field of the channel region during stress conditions.

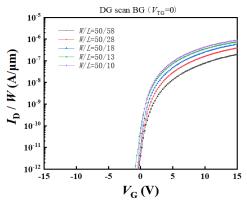

**Fig. 1.** Transfer characteristics of DG TFTs by scanning  $V_{BG}$  with  $V_{TG}$  fixed at 0V.

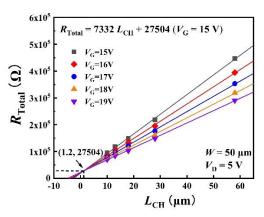

Fig. 2. Source/drain resistance extraction.

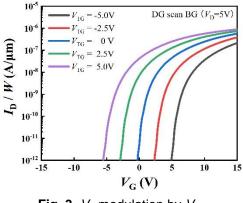

**Fig. 3.**  $V_{\text{th}}$  modulation by  $V_{\text{TG}}$ .

## References

- [1] [1] Abe, K. . "Amorphous In–Ga–Zn–O Dual-Gate TFTs: Current–Voltage Characteristics and Electrical Stress Instabilities." IEEE Transactions on Electron Devices 59.7(2012):1928-1935.

- [2] [1] Jeong, C. Y., et al. "Low-Frequency Noise Properties in Double-Gate Amorphous InGaZnO Thin-Film Transistors Fabricated by Back-Channel-Etch Method." IEEE Electron Device Letters 36.12(2015):1332-1335.

- [3] [1] Qin, Ludong, et al. "P14: The Influence of Bottom gate Dielectric Roughness on the Performance of Double-gate a-GZO Thin Film Transistors." SID Symposium Digest of Technical Papers 50(2019).